芯东西(公众号:aichip001)

作者 | ZeR0

编辑 | 漠影

跨越先进芯片制程的屏障,已然迫在眉睫。

看向全球,半导体产业景气度持续低迷,多家巨头半只脚已迈入寒冬。就连最新财季净利飙涨的全球晶圆代工龙头台积电,也开始使出预警业绩下滑、削减投资预算、关闭4台EUV光刻机、鼓励员工休假的“过冬”连环计。

更大的糟心事还在接踵而至。10月苹果、高通、英伟达、联发科、AMD等台积电大客户的“砍单”余震还没消止,尚未出世的台积电3nm又被曝遭苹果临时“撤单”的暴击,据传台积电已挥刀斩向自家供应链,砍单幅度高达40%~50%。

作为全球先进制程争霸赛中的“头号赢家”,台积电前不久还硬气地向苹果提出涨价,怎么这会儿又颓势尽露?

市场原因是,此前全球信息产业因经历“缺芯”危机而大举抢芯囤芯,提前预定各大晶圆厂不少产能。今年消费电子需求转冷、设备商卖货不畅,唇亡则齿寒,“砍单效应”层层传递至芯片业。

技术原因是,台积电首批3nm的表现“扑街”了。苹果本就对供应链要求严苛且精打细算,结果台积电3nm非但性能参数不达标、良品率低,成本还很高,对苹果来说已经不是一笔划算的买卖。

但这也怪不得台积电,3nm技术之困,其实是当前全球芯片产业都在面临的残酷境地——

随着硅基材料工艺逼近物理极限,技术演进越来越难,仅靠制程工艺的进步,已经带不动芯片性价比的提升了。

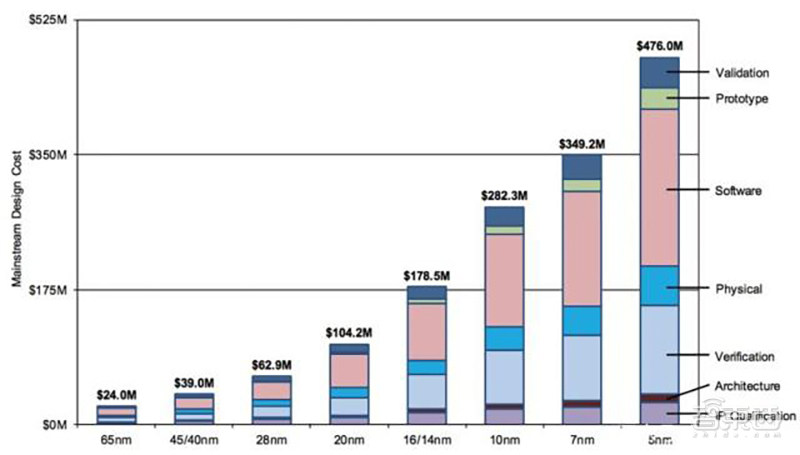

▲芯片流片成本随着制程工艺演进而迅速上升

▲芯片流片成本随着制程工艺演进而迅速上升

不再奉摩尔定律为圭臬的半导体企业们,急需探出一条新路,以跟上旺盛暴涨的算力需求。这也是为什么近年来围绕半导体材料、结构、封装、工具等创新技术路径纷纷走上快车道。

对于中国大陆半导体产业而言,压力更甚一筹。美国政府变本加厉地滥用国家力量,遏制阻滞中国大陆芯片产业的发展。在先进制造相关技术屡遭钳制的背景之下,立足国情扬长避短,整合既有本土优势,探索创新路径,已是燃眉之急。

在中国工程院院士邬江兴看来,比起削足适履,做一双合脚的鞋,才是中国半导体产业的换道超车的机会所在。

而能够绕开先进制程屏障、将系统综合效益显著提升的SDSoW(软件定义晶上系统)技术,也许就是双合脚的鞋。

一、芯片发展面临“三堵墙”,计算架构变革时不我待

在信息化进程下,海量数据爆炸式增长,造成前所未有的数据挑战:算不及、存不下、运不走。

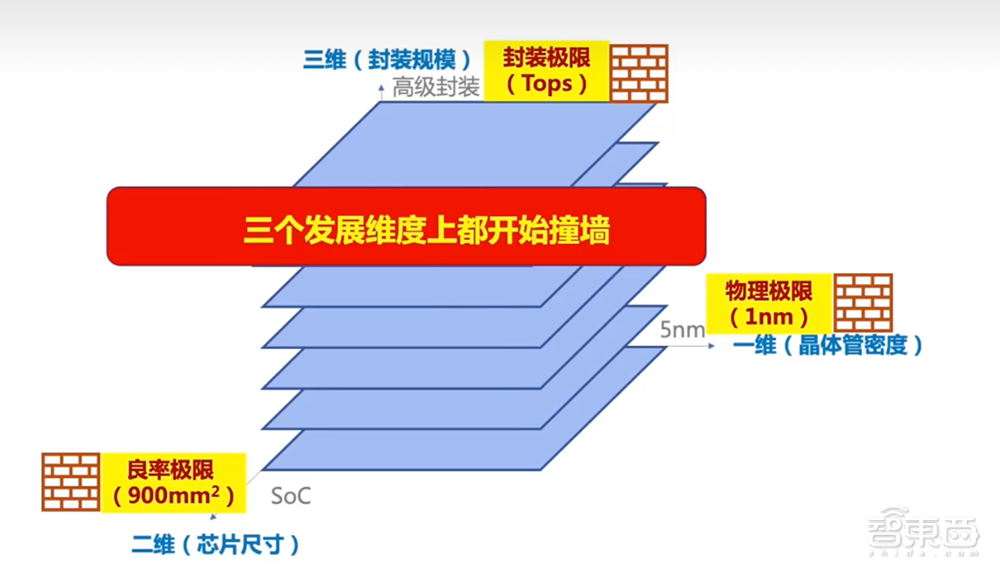

邬江兴院士曾总结当前芯片产业发展面临的“三堵墙”。第一堵墙是物理极限,工艺节点进步逐渐逼近1nm物理极限;第二堵墙是良率极限,单芯片尺寸越做越大,但良率控制越来越难,合格率显著下滑;第三堵墙是封装极限,先进封装技术遭遇散热或规模瓶颈,功耗问题日益凸显,难以支持大规模Die的高级封装。

一方面,登纳德缩放定律失效,摩尔定律放缓,令制程工艺进步对单芯片计算性能的贡献比例不再显著;另一方面,从芯片、模组、机匣、机架到系统,逐层堆叠的工程技术路线面临性能、功耗、时延、可靠性等多方面的发展瓶颈。

我们做个简单推演:芯粒从晶圆被切出来,被封装到模组,多个模组拼成板卡,多个板卡组成机架,众多机架再组成分散到不同机房的集群,随着通信范围扩大,连接越来越稀疏,每过一级传输都会对带宽施加限制,有效的算力、存储力、网络通信力层层折损,能效越来越低。

也就是说,原本芯片能发挥出十成的功力,按照现有的“堆砌式”工程技术路线去走,等到系统层面,它的功力已经折损到只剩下一成。

这就好比建设现代摩天大楼,如果用一块砖头一抹水泥的老办法来堆砌,这栋楼越往上盖承重压力越大,而且根本扛不住地震暴风;要让大楼足够坚固稳定,必须根据超高层建筑结构的受力特点,来设计作为大楼中心支撑的整体钢架。

同样,大型信息基础设施亦是一个复杂精密的系统级工程,要减少从芯片到系统的“逐级插损”,需从计算体系结构层面进行全维创新。

针对这些问题,邬江兴院士带领团队提出了软件定义晶上系统(SDSoW,Software Defined System on Wafer),将大型信息基础设施的工程技术路线从“逐层堆叠式”演进为由异质材料、不同制程工艺的各种芯粒异构集成的“拼接组装式”。

打个比方,“逐层堆叠式”路线像从乡、县到市再到省,一级一级地管理指挥;而“拼接组装式”路线通过将所有芯粒集中放在一块大晶圆上,实现了无插损的扁平化指挥。

据邬江兴院士团队与寒武纪联合测算,基于SDSoW技术路线,在28nm工艺条件下,仅用16块晶圆,就能构建与美国超算Summit同等的算力,同时功耗仅为其1/80、占地面积为其1/16,造价仅为1/5;84块晶圆即可构建E级机器,功耗仅有“堆砌式”系统的1/15、占地面积为其1/18、造价仅为其1/3。

这样对比来看,SDSoW能够将整个大型信息基础设施的综合效益显著提升,对于短期内破解“卡脖子”难题、中长期提供换道超车新路径具有双重战略意义。即便先进工艺及工具受阻,SDSoW也能基于自主可控的国产技术及装备资源,达到领先的系统性能水平。

这一技术路线究竟是怎么实现的?最新技术与生态进展如何?如何助力解决国产芯片自主化的痛点?近日,芯东西与邬江兴院士团队核心成员进行深入交流。

二、结构创新×工艺创新,将异构异质芯粒灵活集成

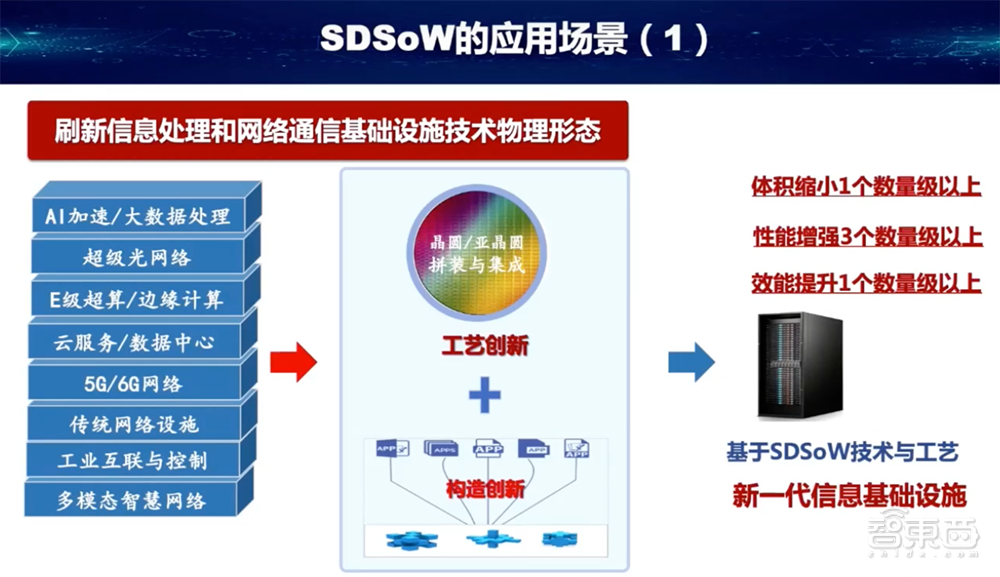

SDSoW既可应用到数据中心、高性能计算、智能计算、算力网络等涉及国计民生的大型信息基础设施,又适用于需执行复杂功能的无人设备,如物联网、网络通信、无人机等。

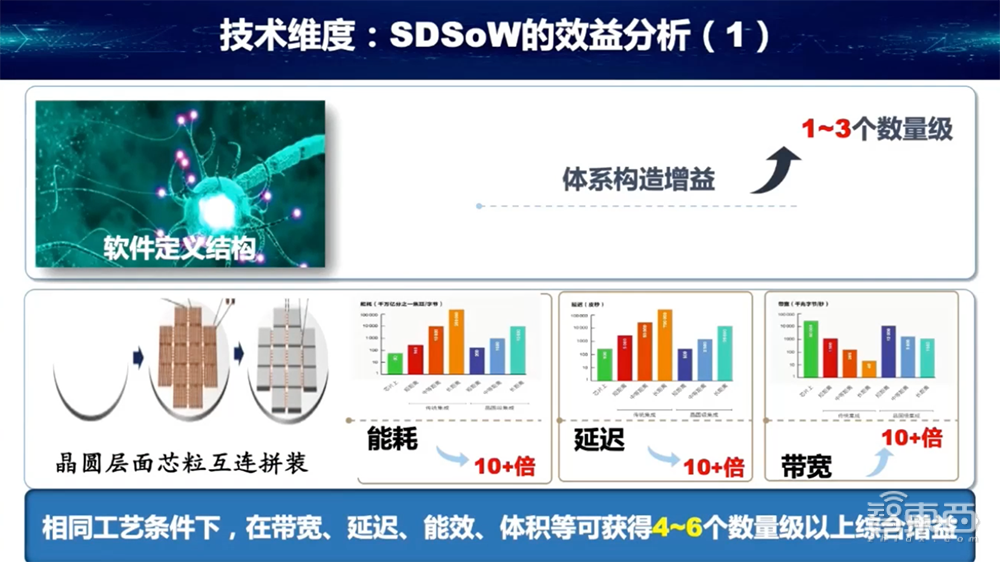

根据邬江兴院士在2020年6月举行的第四届未来网络发展大会上做的演算:在相同工艺条件下,SDSoW有望在带宽、延迟、能效、体积等方面带来4~6个数量级以上的综合增益。

4~6个数量级,来自两大关键组成“SD(软件定义)”和“SoW(晶上系统)”的连乘性增益——

软件定义结构能带来大概1~3个数量级的体系结构增益;晶圆级芯粒互连拼装可将能耗、延迟降为原来的1/10甚至更少,将带宽增加超10倍。

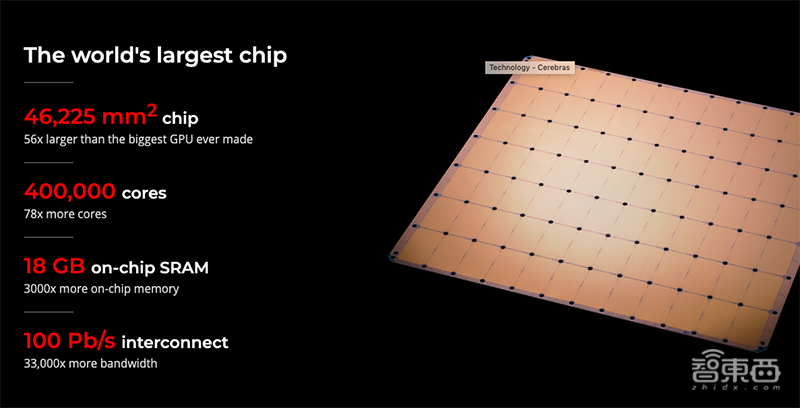

关注芯片设计创新风向的读者,想必会对2019年9月美国AI芯片创企Cerebras Systems推出的世界最大芯片“晶圆级引擎(WSE)”印象深刻。在整块晶圆上集成了40万个AI核心的WSE,便是一个基于晶圆级异构集成技术的SoW典例,最新推出的第二代,单颗晶圆级芯片则集成了85万个AI核心!

▲晶圆级引擎WSE

▲晶圆级引擎WSE

WSE属于同质同构集成,另一个异构集成的SoW典例是美国DARPA在电子复兴(ERI)计划中启动的“通用异构集成和IP重用策略(CHIPS)”项目。该项目通过采用先进封装技术,可将多个不同工艺的Chiplet集成在一起。

但在邬江兴院士团队核心成员看来,Chiplet也许能救某些产业或公司,但不能救中国。

近年来SoW发展突飞猛进,成熟性、经济性、规模性均得到验证,然而目前仍是“戴着镣铐跳舞”,现有相关研究通常基于刚性固定的体系结构,系统内部的计算、存储、IO等资源都是固定的,各资源之间的连接关系和通信带宽也相对固定。

而在实际场景中,不同应用对计算、存储、通信资源的要求各不相同,固化的系统结构在适配不同应用时会存在灵活扩展方面的局限性。

SDSoW相比于SoW的一大差别,便在于此。

在SoW的基础上,SDSoW在芯粒结构、系统、应用3个层面引入“软件定义”,让原本只能赋能一类应用的晶上系统,可利用软件定义硬件满足复杂多样的应用任务需求,将晶上系统丰富的逻辑、存储、网络资源之性能与效能更大程度地释放出来。

“SoW是个三维空间,是个楼群,SD给这个楼群赋予了时间维度的属性,使这个楼群向外展示的服务特性是随时间变化的。”邬江兴院士团队的核心成员解释道,“简单来说,就是一句话,有ASIC级的性能,有FPGA级的灵活性。”

集成了成千上万个芯粒的晶上系统,可以理解成小型云计算规模的计算、存储和网络资源,软件定义则能够让SoW上的所有资源去适应结构,不仅具有云计算服务的集约化效益,而且还有大规模资源灵活变结构的效能增益。

三、软件定义多层优化,SDSoW计算结构详解

SDSoW采用了一种领域专用软硬件协同计算架构,结合了拟态计算和软件定义互连的思想,以综合发挥芯片技术在新结构、新计算、新互连、新集成上的后发优势。

拟态计算是邬江兴院士首创的一项面向领域的高性能、高效能软硬件协同领域专用变结构计算体系理论,让计算结构能主动根据应用需求进行动态重构。据介绍,相较刚性结构计算,变结构计算对计算能效的提升大概在1~3个数量级。

整体来看,SDSoW的体系结构有5层,从下到上依次是硬件资源层、资源感知层、认知决策层、业务感知层、应用层。

▲SDSoW体系结构

▲SDSoW体系结构

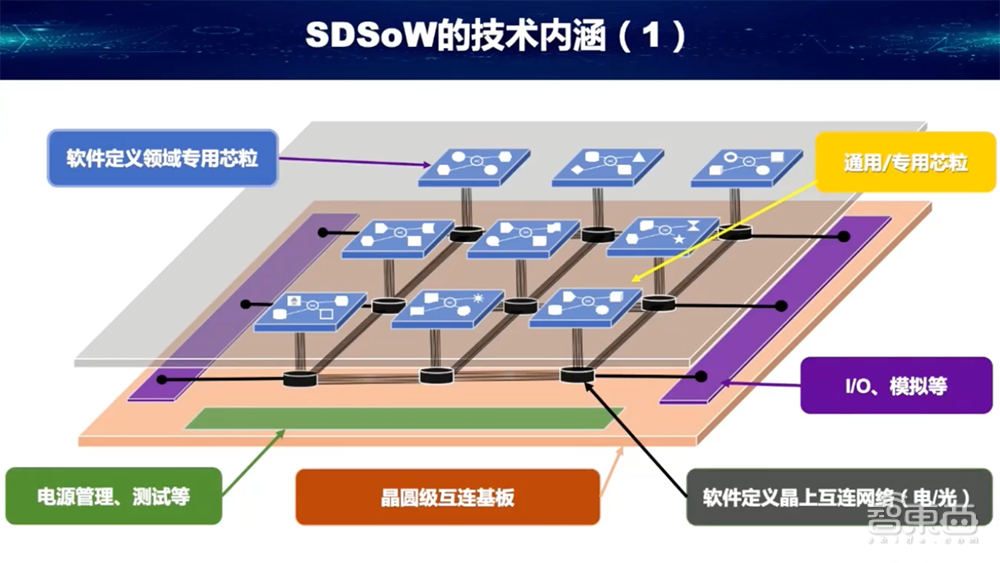

具体来说,这个异构系统包含晶圆级互连基板、晶圆级互连基板上的若干芯粒、用于不同芯粒之间互连的软件定义晶上互连网络。

晶圆级互连基板通过重布线层RDL或光刻方式,提供芯粒之间的互连线路。各芯粒通过TCB(热压焊)与基板连接。预制件的互连将遵循统一的物理接口标准和协议规范,通过晶圆级互连基板和软件定义晶上互连网络进行数据交换。

每个芯粒结构相当于一个“专用FPGA”,根据领域应用功能需求来定制,芯粒结构内的函数化算粒模块以软件定义的方式进行不同的组合和功能重建,从而满足差异化的应用及任务映射需求,实现资源复用。

再往上一层是资源感知层,用于通过感知算法获取硬件资源层各预制件的计算特征及状态信息,并将资源信息传递给认知决策层。业务感知层对目标应用任务进行分解,得到应用任务的计算特征和业务属性,将业务信息反馈给认知决策层。

然后认知决策层依据资源信息、业务信息、调度原则和知识库进行主动决策,动态构建适用于应用任务需求的计算结构,并将该计算结构作为系统配置,作用于硬件资源层。硬件资源层可基于这些系统配置,重构各个预制件之间的组合关系和互连结构。

最后应用层负责提供对各种应用业务的支持。

四、明年落地交换芯片,最快两年打造完整系统

当前SDSoW创新体系结构仍处研发阶段,2020年进入加速发展期,之江实验室已经率先落地了一个先导项目,旨在打通SDSoW的工艺链条。

据邬江兴院士团队核心成员透露,按照乐观估计,如果产业链协同顺利,最快两年可打造出完整SDSoW系统,保守3-5年可实现技术突破。

已有四五十家科研机构及企业参与推进相关项目的落地,包括之江实验室、紫金山实验室、嵩山实验室、海河实验室等。明年之江实验室就会出第一个基于SDSoW工艺流程做出的8T交换芯片,今年一些陆续流片和顶层设计已初步完成。

邬江兴院士团队相信,SDSoW生态发展必须“既不排外,又要有根”,根便是技术创新内核。

以Chiplet为例,SDSoW在接口标准上,既与国际Chiplet产业联盟UCIe兼容,又要高于UCIe标准,通过软件定义支持面向场景的互连协议与互连网络属性,联合学术界、产业界共同提出中国自主创新、自持发展的SDSoW接口与协议标准,并与国内封装厂、晶圆厂合作探索Chiplet相关技术成果如何迁移和复用到SDSoW平台。

待相关流程建立起来,SDSoW才会逐渐走向稳定和规模化。

当然,在应用驱动时代,SDSoW如想发展起来,离不开强需求的应用场景。

从特性来看,SDSoW技术应用到像大型信息基础设施这样的大规模系统能放大其连乘性效益,其软件定义功能亦有助于具备复杂功能的无人设备灵活配置资源。但对于像桌面端这种对功耗和多芯粒要求并不苛刻的应用,具备成本优势的SoC(片上系统)仍将长期占据主流。

邬江兴院士团队核心成员预测,等工艺流程充分成熟与规模化,且开发敏捷性和经济性均优于SoC,SDSoW有可能会在通用桌面等场景替代SoC,届时将实现全产业突破。未来SDSoW亦有望跟类脑计算等新型计算技术结合,实现一些更泛在的科学及工程创新。

他告诉芯东西,未来两类芯片公司预计最有可能成为SDSoW技术方向的主导者。

一类是特色技术明显的芯片公司。他们本身在SoC领域已有生存空间,既能照常产出物理形态的芯片,也能产出SDSoW标准化芯粒产品。

另一类是有强应用场景驱动的大公司。他们足以支持应用级别的系统定义,可基于IDM思路整合各种芯粒和定制晶圆基板,再借助国内系统组装、供电散热和一些成熟工具链来发展SDSoW系统。整个系统开发、调试、敏捷迭代时间都会大幅缩短,成本投入也将降下来。

结语:各立山头绝非上策,形成聚力才能破解困局

受全球经济复苏乏力叠加美国出口管制新规对我国半导体产业的阻滞干扰,全球半导体产业分工体系和布局正在发生深刻调整,中国芯片自主发展的前路更加艰难曲折,但不会因为外界的影响而动摇变化。此时好钢更须用在刀刃上,各立山头只能在局部场景解决局部问题,只有将中国半导体产业的整体资源形成聚力,打造一个中国集成电路的珠峰,才有可能形成对抗的力量。

当前的中国大陆半导体产业,短在先进芯片制造、光刻机等先进设备以及EDA软件,长在芯片设计创新和封测。邬江兴院士团队相信,将结构创新与工艺创新结合的SDSoW,有望将我国半导体产业既有优势协同起来,充分兼顾国内半导体发展水平,趟出一条绕开先进制程等屏障的新路,给国产制造业产能的补位提供缓冲期。

国内半导体现有的存量技术和产业装备,足够支撑SDSoW形成产业闭环,SDSoW是一个“蹦一蹦就能摸得到的篮圈目标”, 属于基于国内工艺链条和设计流程的摸高式创新,关键要看蹦的动力有多大、产业链各环节协同有多紧密。

在人类已进入大工程科研时代,在我国芯片半导体面临极端困难的情况下,我们要发扬“聚是一团火、散是满天星”的精神,尽管SDSoW的前行之路注定崎岖,但对中国而言,却是为数不多可自持发展的“光明之路”,也是我们这个时代的中国半导体人必须要走好的自立自强之路。团结一切可以团结的力量、聚集一切可以聚集的资源,一定能早日开创我国半导体的崭新局面。

SDSoW更多技术细节和专利开放情况,敬请关注将在12月10日举办的第五届软件定义晶上系统技术与产业联盟大会。