芯东西(公众号:aichip001)

编辑 | GTIC

芯东西9月6日报道,在刚刚落幕的GTIC 2022全球AI芯片峰会期间,芯行纪资深研发副总裁丁渭滨以《构建新一代数字实现EDA平台》为主题发表演讲。

新一代EDA产品通过应用AI技术优化客户体验、提升效能是全自动芯片设计迭代的一个重要方向。在数字实现EDA环节,有许多关键的子问题可以得益于丰富的AI模型算法,包括提升布局规划的效率和质量、通过机器学习解决EM-IR和时序之间的相互影响来优化PPA(性能、功耗和面积)、路径分类、拥塞位置预测等。

丁渭滨认为,AI赋能的EDA产品能大幅度提升芯片设计效率,提高性能和EDA可用性。他还分享了芯行纪引入AI技术来构建数字实现EDA平台方面的进展和初步成果。

以下为丁渭滨的演讲实录:

大家下午好。芯行纪是一家数字实现EDA公司,我们专注于自主研发数字实现EDA产品和提供高端设计服务,帮助芯片设计企业更高效便利地开展设计工作。

一、挑战最难赛道,国产EDA新势力涌现

数字实现EDA领域的布局布线部分,是EDA领域中研发难度最大、同时也是市场价值最高的产品之一,只有极少数国际厂商拥有这方面的技术。

那为什么芯行纪敢于去做这个领域的产品,并且要做新一代的数字实现EDA产品?

第一,从时代大背景来看,目前全球科技领域的合作和分工正在急剧变化,现在可能没办法像之前一样互相协同共创,这也就是为什么我们需要自主研发。随着近几年来涌现的EDA方面的内部创新,大家分别开始在不同的方向努力。

芯行纪具备了一支非常专业的团队,集聚了目前在数字实现方面具有非常全面的产品研发经验的先进专家,这几十位“行业老兵”具备超过15年的国际EDA厂商从业经验。我们希望凭借这支优秀的团队,在数字芯片领域贡献一份力量。

第二,目前中国集成电路设计的人才缺口非常大,而其中要培养一个后端工程师尤其不容易。布局布线工具是一个非常庞大的系统,它里面的步骤数量繁多,每个步骤里用人工控制的开关数量可以达到几百个,这些开关之间还可以互相组合,以致于数量更加无限大。

而后端工程师除了要理解设计本身还需要花大量时间来学习如何应用软件,因此一个富有经验的后端设计专家,在市场上实际是不多的。

高度自动化的工具,在某些环节可以节省大量的人力。从这个角度来看,将工具朝自动化乃至智能化方向提升,一定程度上可以缓解人才缺口。

另一方面,目前算力正在不断提升。当现在要架构一个新的软件,你可以用的算力、计算资源和十多年前相比,存在天翻地覆的不同。

早年前能用到的算力无非是一台机器里的多个CPU核,甚至多个CPU核在当时未必流行,而现在的计算机本身的性能提高非常多,网络之间的带宽也提升很高,使得多机之间的协同、并行计算、云计算可能同时存在,传输数据的延迟度大大改善。

现如今存在各式各样的专门类别的计算芯片,对于一些特殊算法,可以通过不同的GPU核或其他IP核,实现指数级的性能提升,这些核的出现同样带来了不一样的机遇。

当你重新思考要做一个布局布线工具的时候,你能够用到的算力和思考的角度就会发生变化,此时你就不会想着做一个工具只在一台单机上跑,而是跳出这个框,思考更多可能性。

二、AI在EDA领域的两大类应用:预测性能,让工具更好用

回到AI这个话题,AI目前在很多行业已经得到了一定的落地,而在EDA领域,利用AI技术改变现有的EDA工具的形态,其实已经在发生。

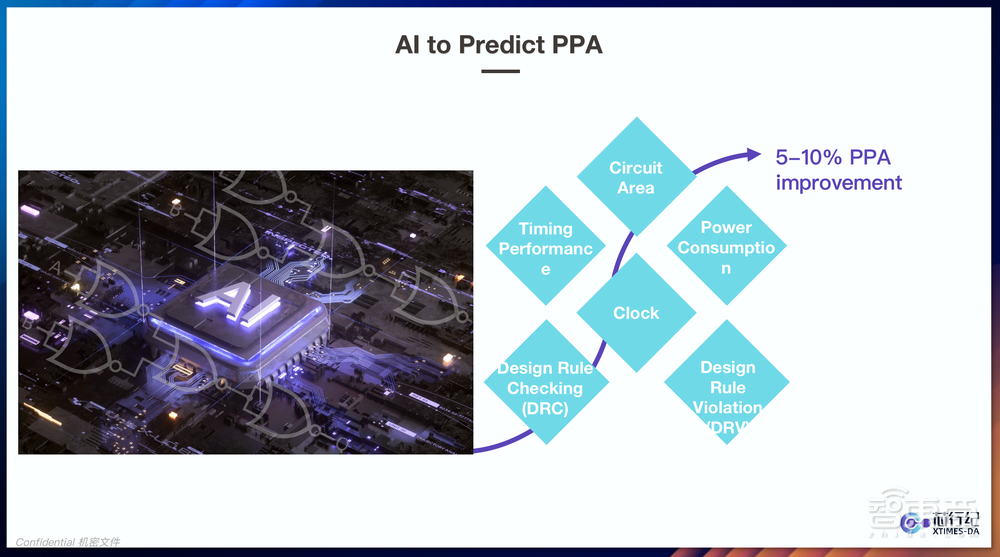

目前AI在EDA工具中的应用主要有两大类。第一类是用AI来预测性能,第二类是借助AI算法帮助EDA工具在使用上更加自动化。

在用AI预测性能方面,因为后端设计的流程很长,在每个阶段看到的性能会局限在当前阶段,当下性能表现并不能说明后面环节的性能一定好,所以如果你希望优化结果真正准确,最好是在当前阶段就能预见到后面环节的结果,如果实现这一步,优化的结果和效率就比较高。

这一点其实已经得到实践,在时序、功耗甚至设计任务方面,顶尖的国际EDA厂商已经把大量步骤转成非传统的启发式方式,通过训练和学习后,可以在前面的阶段预测后面的时序和功耗的变化,这样会得到比较显著的提升效果,比如性能、功耗和面积可以改善5-10%,这是个不小的数字。

简单来说,当一个CPU芯片,频率从原来的2G赫兹提升到2.2G赫兹,这已经是一个非常大的突破。如果你拿这个产品和同质性产品相比,能做到改善10%,你就能占领更多的市场份额。

当然以这样的方式走下去,还存在一定的局限性,但并不是出在AI算法本身,而是在EDA领域我们面对的数据是特殊的,不像一般的图像识别、语音识别这样资料本身可以较容易地获取、分享和测试。

EDA领域的数据都是客户专有数据,处理方式也保密,不同公司之间存在屏障,数据不能互通分享,所以很难综合大量数据训练出更好的模型并继续提升。如何利用已经设计出的芯片,帮助EDA工具更加“聪明”,我想这个还有待继续探讨。

在借助AI算法帮助EDA工具更自动化方面,我们已知当前的EDA工具比较难用,一个后端工程师的工作量有限,但即使是拿着工具反复跑一百次,也无法将智能性带到工具中。

其实理论上来说,当一个设计在反复跑数据时,能够看到哪些参数对应哪些性能,看出参数对应的好坏情况,这意味着当尝试新的设计时,在一定频率、功耗的程度范围内,工具可以基于既有经验帮助做参数推荐。

大家可以仔细想一想,如果我把这件事一直往前推到极致,其实就已经实现无人设计,也就是当重复跑完100次,到了101次想要做一些小修改,需要重新跑流程时,工具可以自动推荐参数,给出在期待和合理范围内的结果。

现在有国际EDA厂商已经在这方面走得较远,在一定程度上可实现技术的落地,输出比人工调参更好的结果。

再往后发展,很有可能出现类似跑工具的机器人,然后变成当大家在购买工具时,还需要同时买机器人,而且是从几家公司同时购买,最后变成几个来自不同EDA厂商的机器人协同设计同一个芯片,我认为这样的可能性是存在的。

毕竟现在人力成本高昂,当用大量的机器取代人力时,能帮助整个公司提高效率、节约成本。

三、智能布局规划:国内首创用AI做拥塞预测,极大节省设计工作量

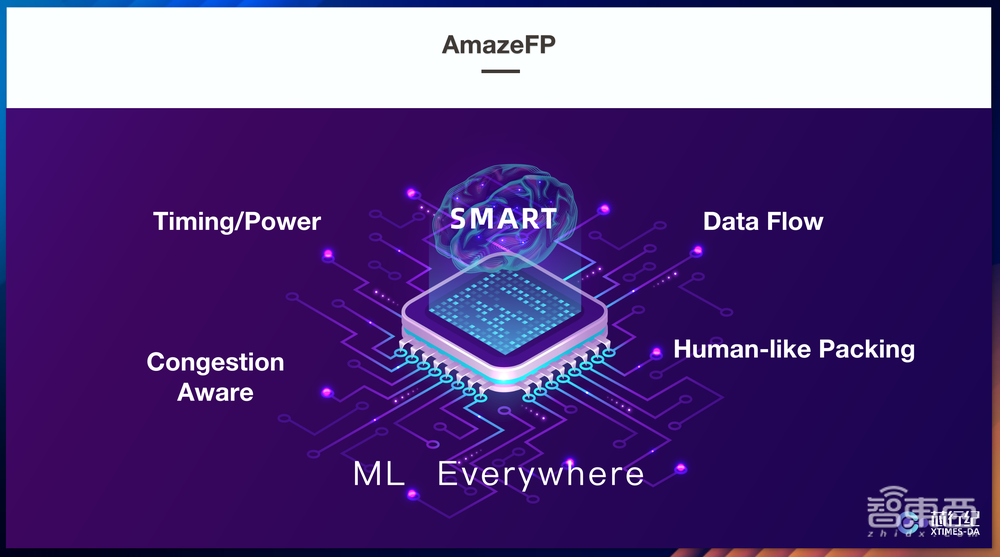

接下来想要和大家分享,芯行纪通过一年多时间的努力做出的成果——智能布局规划工具AmazeFP。

在后端设计中,有一个步骤相对而言还没有比较自动化,就是开局做布局规划的时候,这个时候同时存在很多宏单元和标准单元。标准单元的大小和形状比较规整,此时比较容易用算法来自动摆放,同时因为它的数量相对很多,达到几百万个,目前也不太会有工程师手动摆放。宏单元不同于标准单元,宏单元的大小形状各异,从目前的设计复杂度来看,因为存在各种IP,宏单元的个数比以前多很多。

目前宏单元的摆放主要靠工程师手动摆,有经验的工程师可能对设计比较熟悉就能摆得更好,他可能更清楚哪些宏单元之间沟通较多,可以根据数据流和已有经验进行操作。

但这样也有缺点,首先是当宏单元个数很多时,人工摆放需要耗费大量时间,当存在成百上千个宏单元时,想要手动摆出相对较好的结果其实并不容易。另外,不仅宏单元与宏单元之间有联系,宏单元与标准单元也有联系,摆放时不能只顾两个宏单元,可是一旦要考虑宏单元与标准单元的联系,可能就顾不过来了。

人工摆放有一个优势是会放得比较规矩,但如果同时处理宏单元和标准单元,因为二者存在的大小差异巨大,要实现某种程度上平衡的结果,存在较高的技术门槛。总体而言,从人工和工具摆放的效果来看,人工应该比不过工具摆放的效果。

全世界只有极个别国际EDA厂商可以做到同时捆绑考虑宏单元和标准单元,芯行纪通过自主研发,目前已经实现了这一点。

产品的第二个特点是,我们首创性地将拥塞预测通过机器学习的方式实现。

当前期布局单元时,有一个重要的任务是要确保后期芯片可绕通,否则就需要回头重做。

以前评估拥塞模型时,大家往往采用一种比较粗糙的方式去评估,现在随着工艺的进步,问题变得复杂,特别是到7nm或5nm以下,拥塞的评估一般不会体现在全局,很有可能出现在局部,用以前那些做法可能就看不到拥塞。

此时机器学习就变成了一个选项,当算法学习过大量的制程上的版图模型后,就能够判断哪些位置会有影响。

为什么大多数国际EDA厂商没有把拥塞的预测模型放入布局呢?这里有一个重要的原因。以前用启发式的方式去做,虽然不准,但是很稳定。如果变成机器学习模型,就会发生一些随机事件,结果不够稳定,也很难去控制。

而芯行纪通过大量的艰苦工作,能够用一些独特技术,控制这个模型在某种范围内的稳定性,而它牺牲掉的准度在可以接受的范围内。基于这一前提,我们才能够把这项独有的机器学习拥塞模型放入我们的布局引擎,实现突破。

第三个特点是宏单元自动整理对齐,该功能是拟人化的(human-like)。

当传统工具在做一个布局规划时,不一定非常整齐,它会考虑时序、功耗等各方面因素,将宏单元或标准单元放在推荐的位置,但是当人做设计时,会考虑哪些单元需要靠边或者组合对齐更好,这一点在工具上很难通过传统算法实现,但是通过机器学习可以做到。机器学习是一种模式计算,可以实现版图模型(pattern)的匹配和学习。

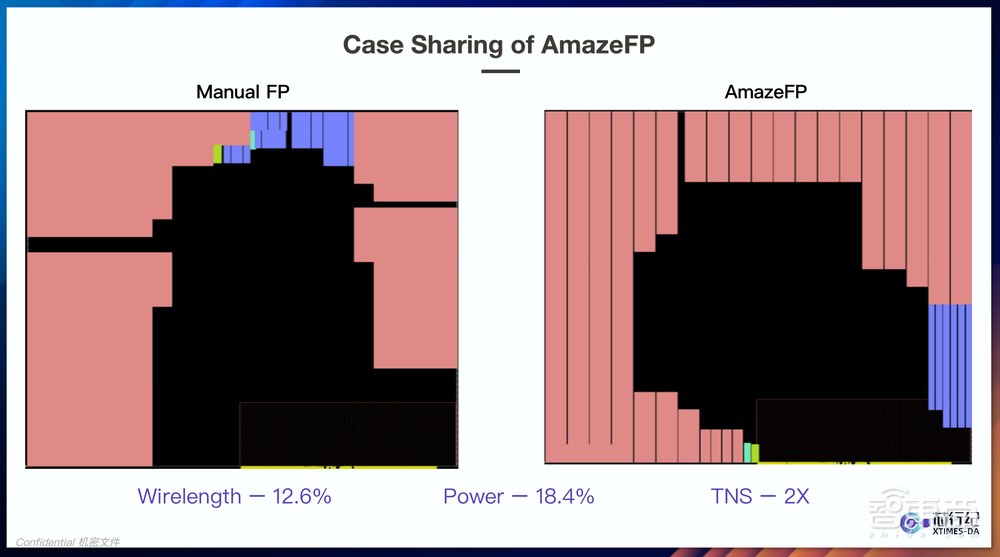

从我们的案例中可以看到,人工摆放的结果很整齐,而我们工具摆放的结果也很整齐,我们的工具会自动将一些单元推到边上,空出留白区域,同时保持比较好的PPA,这可以极大节省设计的工作量。

当某一个案例的布局规划工作时间从以周为记缩短至以小时为记,生产力将成倍提高,释放更多人力用于其他工作。

这就是我们芯行纪近期推出的第一款智能布局规划工具AmazeFP,目前我们正密切与一些客户在合作,我们希望这一工具能够帮助到他们的项目。

当然,AmazeFP只是我们的一个开始,芯行纪的目标是基于3S产品理念(Smart、Speedy、Simple)构建新一代数字实现EDA平台,后期我们全体同仁还将推出更多易用、智能、快速高效的工具。我们也希望携手更多合作伙伴,用我们的EDA产品助力芯片设计企业实现更多的产品成功,谢谢大家。

以上是丁渭滨演讲内容的完整整理。