近日,中科院计算所行业首次发布了报告《专⽤数据处理器 (DPU)白皮书》。DPU(Data Processing Unit)是以数据为中心构造的专用处理器,采用软件定义技术路线支撑基础设施层资源虚拟化,支持存储、安全、服务质量管理等基础设施层服务。DPU正在开启一个巨大的产业化趋势,可以为下一代数据中心、5G边缘计算、云计算提供核心组件。2020年NVIDIA公司发布的DPU产品战略中将其定位为数据中心继CPU和GPU之后的“第三颗主力芯片”,掀起了一波行业热潮。DPU的出现是异构计算的一个阶段性标志。

本期的智能内参,我们推荐中科院计算所的报告《专⽤数据处理器 (DPU)白皮书》, 重点分析DPU产生的背景、技术特征、软硬件参考架构,应用场景和发展趋势。

来源 中科院计算所

原标题:

《专⽤数据处理器 (DPU)白皮书》

作者: 鄢贵海 等

一、什么是DPU?

1、怎么理解DPU的“D”

与GPU的发展类似,DPU是应用驱动的体系结构设计的又一典型案例;但与GPU不同的是,DPU面向的应用更加底层。DPU要解决的核心问题是基础设施的“降本增效”,即将“CPU处理效率低下、GPU处理不了”的负载卸载到专用DPU,提升整个计算系统的效率、降低整体系统的总体拥有成本(TCO)。DPU的出现也许是体系结构朝着专用化路 线发展的又一个里程碑。

DPU中的“D”有三种解释:(1)Data Processing Unit,即数据处理器。这种解释把“数据”放在核心位置,区别于信号处理器、基带处理器等通信相关的处理器对应的“信号”,也区别于GPU对应的图形图像类数据,这里的“数据”主要指数字化以后的各种信息,特别是各种时序化、结构化的数据,比如大型的结构化表格,网络流中的数据包,海量的文本等等。DPU就是处理这类数据的专用引擎。

(2)Datacenter Processing Unit,即数据中心处理器。这种解释把数据中心作为DPU的应用场景,特别是随着WSC(Warehouse-scale Computer)的兴起,不同规模的数据中心成为了IT核心基础设施。目前来看,DPU确实在数据中心中使用前景非常广阔。但是计算中心的三大部分:计算、网络、存储,计算部分是CPU占主导,GPU辅助;网络部分是路由器和交换机,存储部分是高密度磁盘构成的的RAID系统和SSD为代表非易失性存储系统。在计算和网络中扮演数据处理的芯片都可以称之为Datacenter Processing Unit,所以这种说法相对比较片面。

(3)Data-centric Processing Unit,即以数据为中心的处理器。Data-centric,即数据为中心,是处理器设计的一种理念,相对于“Control-centric”即控制为中心。经典的冯诺依曼体系结构就是典型的控制为中心的结构,在冯诺依曼经典计算模型中有控制器、计算器、存储器、输入和输出,在指令系统中的表现是具有一系列非常复杂的条件跳转和寻址指令。而数据为中心的理念与数据流(Data Flow)计算一脉相承,是一种实现高效计算的方法。同时,现在试图打破访存墙(Memory Wall)的各种近存(Near-memory)计算、存内(In-memory)计算、存算一体等技术路线,也符合数据为中心的设计理念。

总体来说,DPU有四大应用方向,应用于网络、存储和安全场景:

1、DPU最直接的作用是作为CPU的卸载引擎,接管网络虚拟化、硬件资源池化等基础设施层服务,释放CPU的算力到上层应用;

2、DPU可以成为新的数据网关,将安全隐私提升到一个新的高度。在网络环境下,网络接口是理想的隐私的边界,但是加密、解密算法开销都很大,例如国密标准的非对称加密算法SM2、哈希算法SM3和对称分组密码算法SM4。如果用CPU来处理,就只能做少部分数据量的加密。在未来,随着区块链承载的业务的逐渐成熟,运行共识算法POW,验签等也会消耗掉大量的CPU算力。而这些都可以通过将其固化在DPU中来实现,甚至DPU将成为一个可信根。

3、DPU也可以成为存储的入口,将分布式的存储和远程访问本地化。随着SSD性价比逐渐可接受,部分存储迁移到SSD器件上已经成为可能,传统的面向机械硬盘的SATA协议并不适用于SSD存储,所以,将SSD通过本地PCIe或高速网络接入系统就成为必选的技术路线。

4、DPU还可以成为算法加速的沙盒,成为最灵活的加速器载体。DPU不完全是一颗固化的ASIC,在CXL、CCIX等标准组织所倡导CPU、GPU与DPU等数据一致性访问协议的铺垫下,将更进一步扫清DPU编程障碍,结合FPGA等可编程器件,可定制硬件将有更大的发挥空间,“软件硬件化”将成为常态,异构计算的潜能将因各种DPU的普及而彻底发挥出来。

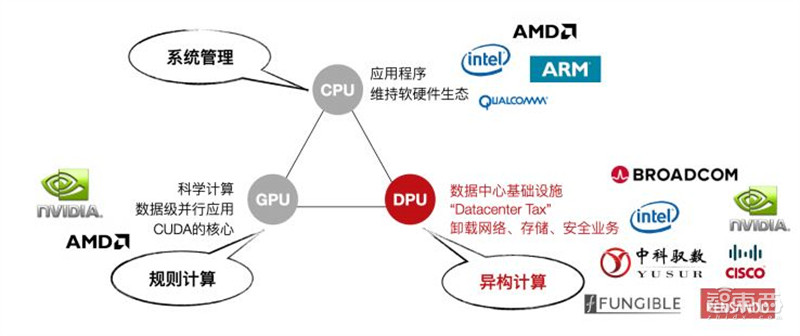

2、DPU与CPU、GPU的关系

CPU是整个IT生态的定义者,无论是服务器端的x86还是移动端的ARM,都各自是构建了稳固的生态系统,不仅形成技术生态圈,还形成了闭合价值链。

GPU是执行规则计算的主力芯片,如图形渲染。经过NVIDIA对通用GPU(GPGPU)和CUDA编程框架的推广,GPU在数据并行的任务如图形图像、深度学习、矩阵运算等方面成为了主力算力引擎,并且成为了高性能计算最重要的辅助计算单元。2021年6月公布的Top500高性能计算机(超级计算机)的前10名中,有六台(第2、3、5、6、8、9名)都部署有NVIDIA的GPU。

▲未来算⼒⽣态(相关⼚商为不完全列举,仅做为⽰意参考)

数据中心与超极计算机不同,后者主要面向科学计算,如大飞机研制,石油勘探、新药物研发、气象预报、电磁环境计算等应用,性能是主要指标,对接入带宽要求不高;但数据中心面向云计算商业化应用,对接入带宽,可靠性、灾备、弹性扩展等要求更高,与之相适应发展起来的虚拟机、容器云、并行编程框、内容分发网等等技术,都是为了更好的支撑上层商业应用如电商、支付、视频流、网盘、办公OA等。但是这些IaaS和PaaS层的服务开销极大,Amazon曾公布AWS的系统开销在30%以上。如果需要实现更好的QoS,在网络、存储、安全等基础设施服务上的开销还会更高。

这些基础层应用类型与CPU架构匹配程度不高导致计算效率低下。现有的CPU的架构有两个大类:多核架构(数个或数十几个核)和众核架构(数百个核以上),每种架构支持唯一的规范通用指令集之一,如x86、ARM等。以指令集为界,软件和硬件被划分开来分别独立发展,迅速的催生了软件产业和微处理器产业的协同发展。

但是,随着软 件复杂度的上升,软件的生产 率(Productivity)得到更多的重视,软件工程学科也更加关注如何高效地构建大型软件系统,而非如何用更少的硬件资源获得尽可能高的执行性能。业界有个被戏称的“安迪比尔定律”,其内容是“What Andy gives, Bill takes away”,安迪(Andy)指英特尔前CEO安迪·格鲁夫,比尔(Bill)指微软前任CEO比尔·盖茨,意为硬件提高的性能,很快被软件消耗掉了。

正如CPU在处理图像处理时不够高效一样,现在有大量的基础层应用CPU处理起来也比较低效,例如网络协议处理,交换路由计算,加密解密,数据压缩等这类计算密集的任务,还有支持分布式处理的数据一致性协议如RAFT等。这些数据或者通过从网络IO接入系统,或者通过板级高速PCIe总线接入系统,再通过共享主存经由DMA机制将数据提供给CPU或GPU来处理。既要处理大量的上层应用,又要维持底层软件的基础设施,还要处理各种特殊的IO类协议,复杂的计算任务让CPU不堪重负。

这些基础层负载给“异构计算”提供了一个广阔的发展空间。将这些基础层负载从CPU上卸载下来,短期内可以“提质增效”,长远来看还为新的业务增长提供技术保障。DPU将有望成为承接这些负载的代表性芯片,与CPU和GPU优势互补,建立起一个更加高效的算力平台。可以预测,用于数据中心的DPU的量将达到和数据中心服务器等量的级别,每年千万级新增,算上存量的替代,估算五年总体的需求量将突破两亿颗,超过独立GPU卡的需求量。每台服务器可能没有GPU,但必须有DPU,好比每台服务器都必须配网卡一样。

3、异构计算的阶段性标志

DPU的出现是异构计算的又一个阶段性标志。摩尔定律放缓使得通用CPU性能增长的边际成本迅速上升,数据表明现在CPU的性能年化增长(面积归一化之后)仅有3%左右,但计算需求却是爆发性增长,这几乎是所有专用计算芯片得以发展的重要背景因素。

摩尔定律的放缓与全球数据量的爆发这个正在迅速激化的矛盾通常被作为处理器专用化的大背景,正所谓硅的摩尔定律虽然已经明显放缓,但“数据摩尔定律”已然到来。IDC的数据显示,全球数据量在过去10年年均复合增长率接近50%,并进一步预测每四个月对于算力的需求就会翻一倍。

因此必须要找到新的可以比通用处理器带来更快算力增长的计算芯片,DPU于是应运而生。这个大背景虽然有一定的合理性,但是还是过于模糊,并没有回答DPU之所以新的原因是什么,是什么“量变”导致了“质变”?

从现在已经公布的各个厂商的DPU架构来看,虽然结构有所差异,但都不约而同强调网络处理能力。从这个角度看,DPU是一个强IO型的芯片,这也是DPU与CPU最大的区别。CPU的IO性能主要体现在高速前端总线(在Intel的体系里称之为FSB,Front Side Bus),CPU通过FSB连接北桥芯片组,然后连接到主存系统和其他高速外设(主要是PCIe设备)。目前更新的CPU虽然通过集成存储控制器等手段弱化了北桥芯片的作用,但本质是不变的。

DPU的IO带宽几乎可以与网络带宽等同,例如,网络支持25G,那么DPU就要支持25G。从这个意义上看,DPU继承了网卡芯片的一些特征,但是不同于网卡芯片,DPU不仅仅是为了解析链路层的数据帧,而是要做直接的数据内容的处理,进行复杂的计算。所以,DPU是在支持强IO基础上的具备强算力的芯片。简言之,DPU是一个IO密集型的芯片;相较而言,DPU还是一个计算密集型芯片。

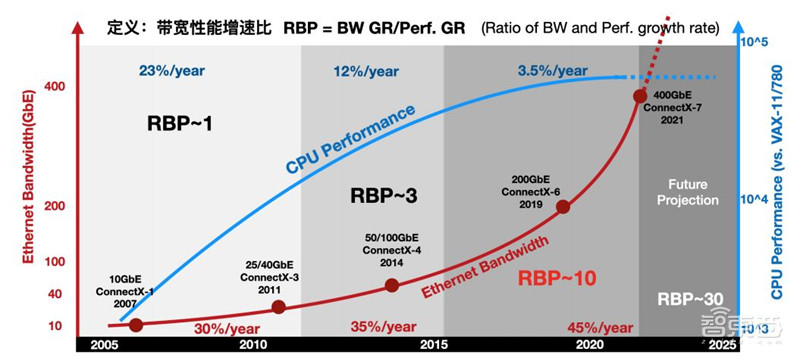

进一步地,通过比较网络带宽的增长趋势和通用CPU性能增长趋势,能发现一个有趣的现象:带宽性能增速比(RBP,Ratio of Bandwidth andPerformance growth rate)失调。RBP定义为网络带宽的增速比上CPU性能增速,即RBP=BW GR/Perf. GR如下图所示,以Mellanox的ConnectX系列网卡带宽作为网络IO的案例,以Intel的系列产品性能作为CPU的案例,定义一个新指标“带宽性能增速比”来反应趋势的变化。

▲带宽性能增速⽐(RBP)失调

2010年前,网络的带宽年化增长大约是30%,到2015年微增到35%,然后在近年达到45%。相对应的,CPU的性能增长从10年前的23%,下降到12%,并在近年直接降低到3%。在这三个时间段内,RBP指标从1附近,上升到3,并在近年超过了10!如果在网络带宽增速与CPU性能增速近乎持平,RGR~1,IO压力尚未显现出来,那么当目前RBP达到10倍的情形下,CPU几乎已经无法直接应对网络带宽的增速。RBP指标在近几年剧增也许是DPU终于等到机会“横空出世”的重要原因之一。

4、DPU发展历程

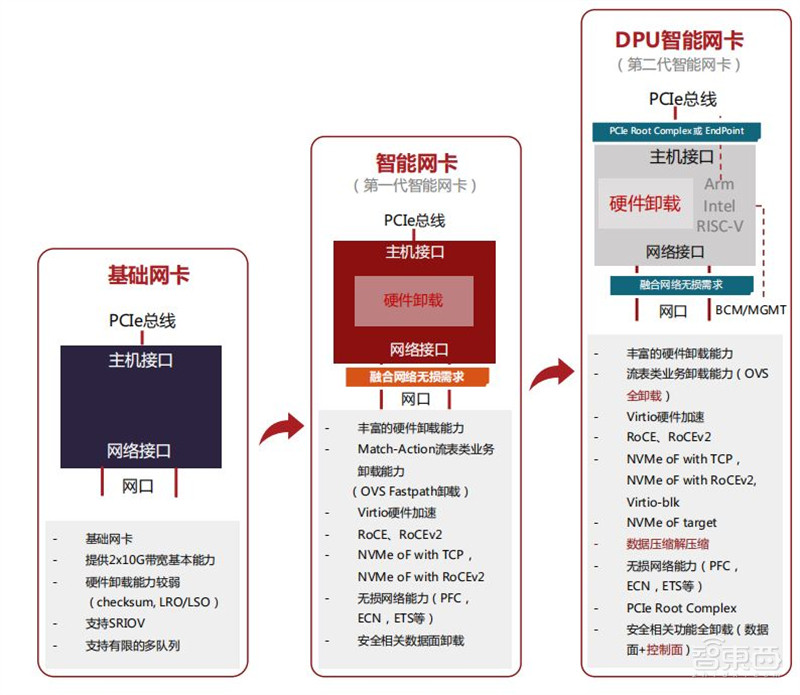

随着云平台虚拟化技术的发展,智能网卡的发展基本可以分为三个阶段:

▲智能⽹卡发展的三个阶段

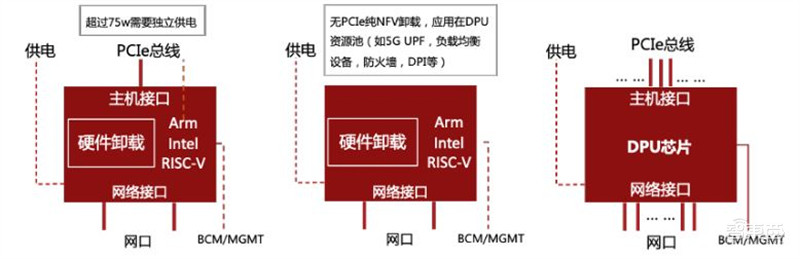

随着越来越多的功能加入到智能网卡中,其功率将很难限制在75W之内,这样就需要独立的供电系统。所以,未来的智能网卡形态可能有三种形态:

(1)独立供电的智能网卡,需要考虑网卡状态与计算服务之间低层信号识别,在计算系统启动的过程中或者启动之后,智能网卡是否已经是进入服务状态,这些都需要探索和解决。

(2)没有PCIe接口的DPU智能网卡,可以组成DPU资源池,专门负责网络功能,例如负载均衡,访问控制,防火墙设备等。管理软件可以直接通过智能网卡管理接口定义对应的网络功能,并作为虚拟化网络功能集群提供对应网络能力,无需PCIe接口。

(3)多PCIe接口,多网口的DPU芯片。例如Fungible F1芯片,支持16个双模PCIe控制器,可以配置为Root Complex模式或Endpoint模式,以及8x100G网络接口。通过PCIe Gen3 x8接口可以支撑8个Dual-Socket计算服务器,网络侧提供8x100G带宽的网口。

▲未来智能⽹卡的硬件形态

DPU作为一种新型的专用处理器,随着需求侧的变化,必将在未来计算系统中成为一个重要组成部分,对于支撑下一代数据中心起到至关重要的作用。

5、产业化机遇

数据中心作为IT基础设施最重要的组成部分在过去10年成为了各大高端芯片厂商关注的焦点。各大厂商都将原有的产品和技术,用全新的DPU的理念重新封装后,推向了市场

NVIDIA收购Mellanox后,凭借原有的ConnectX系列高速网卡技术,推出其BlueField系列DPU,成为DPU赛道的标杆。作为算法加速芯片头部厂商的Xilinx在2018年还将“数据中心优先(Datacenter First)”作为其全新发展战略。发布了Alveo系列加速卡产品,旨在大幅提升云端和本地数据中心服务器性能。

2019年4月,Xilinx宣布收购Solarflare通信公司,将领先的FPGA、MPSoC和ACAP解决方案与 Solarflare 的超低时延网络接口卡( NIC )技术以及应用加速软件相结合,从而实现全新的融合SmartNIC解决方案。Intel 2015年底收购了Xilinx的竞争对手——Altera,在通用处理器的基础上,进一步完善硬件加速能力。

Intel 2021年6月新发布的IPU产品(可以被视为Intel版本的DPU),将FPGA与Xeon D系列处理器集成,成为了DPU赛道有力的竞争者。IPU是具有强化的加速器和以太网连接的高级网络设备,它使用紧密耦合、专用的可编程内核加速和管理基础架构功能。

IPU提供全面的基础架构分载,并可作为运行基础架构应用的主机的控制点,从而提供一层额外防护。几乎同一时间,Marvall发布了OCTEON 10DPU产品,不仅具备强大的转发能力,还具有突出的AI处理能力。

在同 一时期, 一些传统并不涉足芯片设计的互联网厂商,如海外的Google、Amazon,国内的阿里巴巴等巨头纷纷启动了自研芯片的计划,而且研发重点都是面向数据处理器的高性能专用处理器芯片,希望以此改善云端的服务器的成本结构,提高单位能耗的性能水平。数据研究预测DPU在云计算市场的应用需求最大,且市场规模随着云计算数据中心的迭代而增长,到2025年单中国的市场容量都将达到40亿美元的规模。

二、业界产品概要

1、NVIDIA BlueField

NVIDIA推出的BlueField系列DPU,在支持网络处理、安全和存储功能的同时,实现网络虚拟化、硬件资源池化等基础设施层服务。BlueField DPU既是一个承担高带宽(100Gbs/200Gbs/400Gbs)的网络处理器,同时也是一个独立的嵌入式处理器,它管理着众多加速器引擎,比如加密解密、正则表达式匹配以及存储加速等等。BlueField DPU也可以通过ARM核运行嵌入式Linux系统,处理一定控制面的任务,具有一定的通用能力。

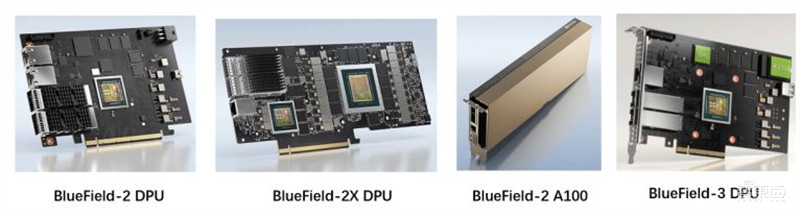

NVIDIA 2020年推出BlueField-2系列 DPU,并计划在2022年推出性能更强的BlueField-3 DPU。

▲BlueField 系列DPU

BlueField-2 DPU具有ConnectX-6的网络处理功能,可支持高速以太网(200Gb/s)或 InfiniBand两种接口, 八个ARM核,高带宽DRAM和PCIe交换机,通过高速Mesh网络连接在一起。包含支持网络、存储、加密、流媒体等计算的专用加速器,同时具有面向安全、虚拟化、硬件隔离和远程管理的功能。

BlueField-2X DPU相比于BlueField-2 DPU,增加了对AI功能的支持,融合NVIDIA Ampere 架构的GPU并行处理能力与BlueField-2 DPU的数据处理能力。BlueField-3 DPU是第三代NVIDIA DPU。与BlueField-2 DPU相比,设计支持400Gb/s以太网或NDR InfiniBand网络连接,也可以卸载、加速和隔离软件定义的网络、存储、安全和管理功能,从而提高数据中心的性能、效率和安全性。

2、Intel IPU(Mount Evans)

IPU(Infrastructure Processing Unit)是一种具有强化加速和以太网连接的网络设备,可使用紧密耦合的专用可编程内核来加速和管理基础设施。 IPU提供完整的基础设施卸载,并通过充当运行基础设施应用程序的主机的控制点来提供额外的安全层。通过使用IPU,可以从服务器卸载与运行基础设施任务相关的开销。云服务供应商(cloud service provider,CSP)软件在IPU本身上运行,而租户的应用程序在服务器CPU上运行。这不仅释放了服务器上的资源,同时优化了整体性能,而且为CSP提供了一个单独且安全的控制点。

IPU将基于硬件的数据路径(包括 FPGA)与处理器内核相结合,使得基础设施以硬件的速度处理,能够跟上不断提高的网络速度和软件实现控制平面功能的灵活性。IPU具有以下三个优势:基础设施功能和租户工作负载物理分离允许用户完控制CPU;供应商可以将基础设施任务完全卸载给IPU,有助于提高CPU资源利用率,最大化收益;实现完全无磁盘服务器架构的云数据中心。

随着基础设施和租户业务的物理分离,通过加速器可以有效地卸载基础设施功能,并将其转移到真正的无磁盘架构。Intel认为IPU将成为未来数据中心架构的核心组件,在2021年的Intel Architecture Day上,Intel推出了基于FPGA和ASIC的两种实现方式的产品。其中,Oak Springs Canyon和Arrow Creek是针对云和通信的基于FPGA的IPU产品,Mount Evans是基于ASIC的IPU产品。目前,相关产品的技术细节还未对外公布。

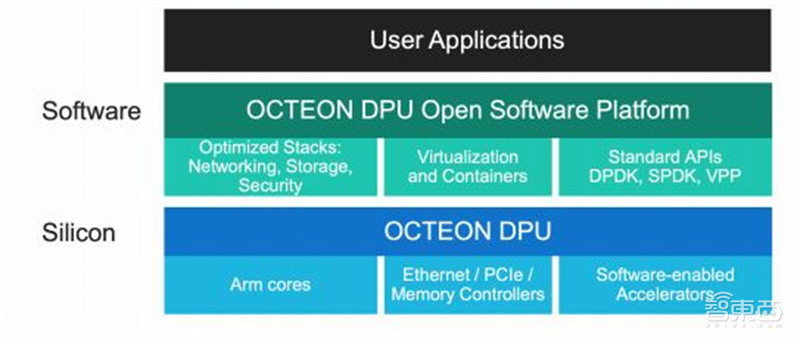

3、Marvell OCTEON

2021年6月28日Marvell发布了基于5nm工艺的OCTEON 10系列DPU,搭载了算力强劲的ARM Neoverse N2核,并且配备了多种硬件加速模块,包括加解密、包处理及人工智能推理加速器。同时为了提供用户友好的可编程接口,提高应用开发效率,Marvell配套硬件设计了包括DPDK、Marvell ML toolchain等在内的软件开发平台。

▲Marvell OCTEON 10系列DPU

OCTEON 10子产品包括CN103,CN106,CN106S 和DPU 400,不同子产品间的主要区别在于集成的ARM Neoverse N2核数,核数越多,性能越强的同时功耗也相对越大(不高于60W)。目前OCTEON 10 系列DPU产品形式主要为芯片及其配套开发平台(如图5-8),开发平台预计于2021年第四季度面世。四款子产品仅公布了其核心技术特征,具体产品细节及形式尚未披露。

▲OCTEON 10 DPU芯⽚(左)及其开发平台(右)

4、Fungible DPU

针对以数据为中心(data-centric)应用的处理,Fungible研发了F1 DPU处理器和TrueFabric互联技术。TrueFabric是由Fungible首先提出的新型大规模数据中心网络互联标准,这种Fabric互联协议基于标准的UDP/IP/Ethernet协议栈构建。

RoCEv2是一种当前数据中心网络中主流的互联网络协议,该协议同样基于UDP/IP/Ethernet搭建,对终端提供高性能的RDMA Read/Write服务,而TrueFabric对接入点提供高性能的Send/Receive服务。Fungible F1 DPU原生支持TrueFabric,因此F1 DPU可以用于大规模TrueFabric数据中心网络,不同类型的服务器都可以将Fungible DPU作为网络接入点。

5、中科驭数 K2 DPU

核处理器(Kernel Processing Unit,KPU)是中科驭数原创的软件定义计算架构,专为加速特定领域核心功能计算而设计的一种协处理器架构。KPU以功能核作为基本单元,直接对应用中计算密集型应用进行抽象核和高层综合,实现以数据为中心的架构“定制”。KPU具有超强异构核集成和调度能力,一颗KPU根据需求可以集成数十至数百个功能核。在运行机制上,KPU采用“数据驱动并行计算”的方式,运行过程中通过数据流来激活不同的功能核进行相应计算。

通过软件定义的方式用户可以灵活的建立“功能核”与应用层运算之间的关系,从而实现“功能核”到运算需求的“一对一”服务,保证计算效率。且不同于FPGA在电路层的改造的性能牺牲,KPU的核心技术在功能核层,功能核来自于对于计算模式的抽象,并将其IP化。通过高层次综合,既实现了领域内硬件的统一,降低了规模限制的硬件成本和设计周期,又能通过软件编程实现不同功能的计算;特定需求只需要增删功能核的种类和数量即可。在整体计算效率提升百倍的前提下,仍然具有非常高的可扩展性和灵活性。

目前中科驭数已经完成了四类KPU芯片架构设计,1)KPU-Swift针对网络协议处理设计;2)KPU-Conflux针对时间序列/大数据分析设计;3)KPU-Trusy针对安全领域处理设计,4)KPU-FlexFlow针对智能计算设计。并在5个应用领域积累了80余类功能核。

中科驭数在2019年完成第一代KPU芯片K1流片,针对序列数据处理及数据库/大数据分析而设计。集成了序列卷积tscov、序列滤波tsfir、序列距离tsdist、序列相似tsdtw等20多类功能核。相比于传统软件解决方案,基于驭数K1的加速方案在数据库/大数据分析,以及时间序列处理等业务场景中可获得超2个数量级的性能提升。

三、DPU未来展望

工业和信息化部发布的《新型数据中心发展三年行动计划(2021-2023年)》中明确提出要加快提升算力算效水平,“推动CPU、GPU等异构算力提升,逐步提高自主研发算力的部署比例”,“加强专用服务器等核心技术研发”,“树立基于5G和工业互联网等重点应用场景的边缘数据中心应用标杆”等等。

该行动计划也部分反映了DPU等新型算力芯片难得的历史发展机遇。虽然国内厂商在芯片产品化的环节还相比国外一线厂商还有差距,但是在DPU架构的理解上还是有独到的见解的,而且我国目前在数据中心这个领域,无论是市场规模还是增速,特别是用户数量,相较于国外都有巨大的优势。国内厂商有望充分利用这一“应用势能”,加快发展步伐,在DPU这个赛道与国外厂商逐鹿中原。

DPU的潜在市场非常巨大,预测到2025年仅中国市场就能达到每年40亿美元的规模,估计全球将超过120亿美元,但挑战与机遇并存。IaaS在国内云服务市场占比约60%,支撑了目前最重要的PaaS的容器云技术。未来几年,我国仍将维持IaaS为主的云计算结构,预计市场占比将逐上升到70%。

目前要解决DPU标准化应用,还存在一定挑战。由于数据中心本身的复杂性,各大厂商一方面采用COTS组件来构建系统,追求低成本,一方面又设法分层服务化(IaaS,PaaS,SaaS),打造面向不用类型客户的标准化产品,但除此之外的所有技术实现几乎都是各家“八仙过海,各显神通”,如AWS有Nitro,阿里云有MOC。有的厂商强化IO能力、有的关注路由转发、有的重视存储卸载、有的关注安全加密——不一而足。例如各大公有云厂商、电信运营商等都有比较完整、也比较封闭的底层架构和应用生态。上层负载不同,必然对底层架构有各异的需求,这也许是目前DPU标准化面临的最大的挑战。

DPU作为一类专用处理器,与通用CPU的发展路径可能会有所不同。专用计算体系结构和通用计算体系结构的阵地是不同的,专用计算竞争的焦点是数据平面,而通用计算竞争的焦点是控制平面。专用计算好比是造赛车,目标就是“快”,重点是根据赛道的类型来决定赛车的结构;通用计算好比是造民用车,目标更加的多元化,不仅要兼顾不同路况下的可用性,还要考虑性价比、代际兼容性等等。所以,以通用CPU的标准来看待DPU可能并不合适,甚至会制约了专用DPU的发展。一个有商业价值的技术必须建立在“技术闭环”的基础上:锚定需求、研发、使用、反馈、再研发改进、再扩大使用范围……,即所谓“先垂直深耕,再水平扩展”的发展战略可能更适合DPU的发展。技术只有投入使用才能体现价值,有使用价值才有可能商业化,才能完成技术闭环到商业闭环的进化。

技术闭环的形成需要集中火力打穿到应用才能铺就。碎片化并不是“专用”障碍,反而应该是专用技术路线充分利用的优势。当然,传统的“one-size-fit-all”的ASIC商业模式,通过上量来摊薄芯片研发的巨额NRE成本本身还是有效的,所以专用DPU最终也要谋求“水平扩展”来覆盖更多的场景,还是要尽可能把各异的需求整合起来,并且适应不同厂商的数据中心架构,但这必将是一个长期而艰巨的任务。DPU肯定不算是一个“低垂的果实”,各个DPU厂商可能不能寄期望于当前“需求各异、体系封闭”的局面自发地在短期内变得“整齐划一,全面开放”,只能是在竞争合作的博弈过程中,逐渐满足越来越多的行业需求。放弃幻想,步步为营,“结硬寨,打呆仗”,这需要长期行业“Knowhow”的整合和持续的产品迭代。

更需要上下游企业共同来构建良性、开放的生态环境,按照基础性技术研发的规律来研发DPU,面向网络、安全、存储、虚拟化等基础技术,划分好逻辑层次,利用好“软件定义”的思想,构造一个完整的DPU软硬件体系。而不是把DPU当成普通的算法加速器,只谋求解决一些碎片化的需求。从目前行业的关注度来看,DPU带来的机遇已经基本形成共识,期待在这一趋势的驱使下,行业内的各个厂商协同起来,将DPU这一创新的产品早日赋能各行各业,成为新的生产力。

智东西认为,在英伟达的带领下,今年DPU的概念非常火爆,这也说明了在摩尔定律即将走向终结的大背景下,通过工艺提升来提高芯片性能、成本等的方式已经不复存在。新时代的信息革命需要剑走偏锋,用新的计算架构来满足庞大的运算和数据的需求。