智东西(公众号:zhidxcom)

编 | 云鹏

智东西11月22日消息,三星在昨天的一个更新补丁中,透露了其自研的最新定制CPU核心M5的部分细节信息,包括相较于前代M4的升级点,以及基础架构图示。M5是三星自研定制核心的第五代产品。

三星上月发布了最新一代7nm旗舰SoC芯片Exynos 990,性能增强20%,其中就使用了自家的2颗猫鼬M5核心。据三星消息,Exynos 990今年年底将实现量产,并于明年用在旗舰机型上。

本月初,三星宣布放弃自研CPU核心,将关闭CPU核心研发部门,未来的Exynos处理器全部使用ARM架构,至此,M5也成为了三星最后一个自研定制核心。以下是外媒对此次M5细节报道的原文编译。

一、IPC改进不明显

M5是由三星奥斯汀研发中心(SARC)开发的三星第五代定制内核。考虑到最近的裁员和内部重组浪潮,它也即将成为SARC研发的最后一个定制核心。

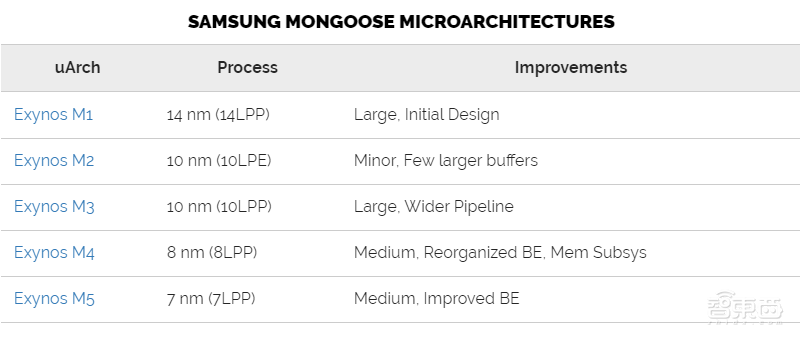

▲M5改进情况概述

三星表示,M5内核可提供“高达20%的增强性能”,所以平均水平应该会相对更低。尽管LLVM调度器模型的级别较高,无法说明发生了哪些较小的修改,但我们可以看到一些较大的改动。

从LLVM补丁程序中,我们很难看到M5的大部分性能提升来自于IPC的改进,除非这些性能提升来自于显着改进的预取器(prefetchers),分支预测器(branch predictors)或其他类似的隐藏组件。

二、指令集队列增加

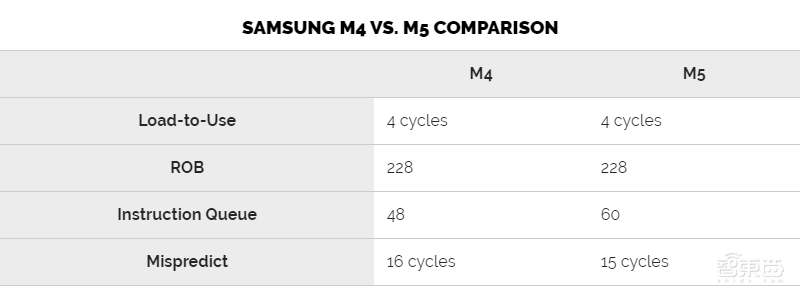

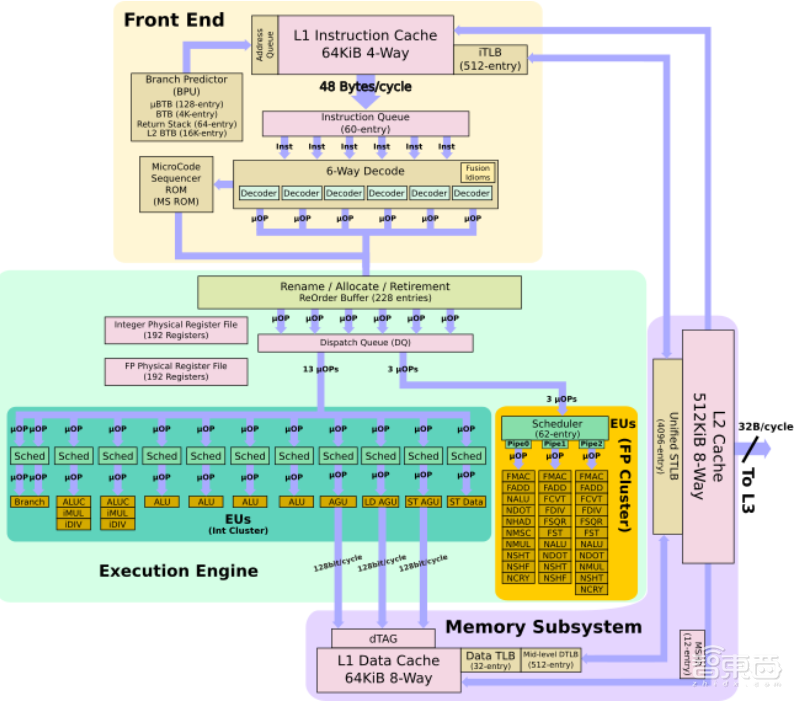

在指令集方面,M5具有与M4 – Armv8.2-A相同的ISA级别。在较高的层次上,M5也与M4十分相似:通道(pipeline)保持6宽(wide)解码,后端保留相同的228条深度重排序缓冲区(deep reorder buffer)。

三星确实将指令队列从48个条略微增加到60个,而更大的变化是错误预测损失(misprediction penalty)改善了1个周期,降低到15个周期。

▲M5与M4的参数对比

▲M5架构示意图

三、后端浮点性能改善

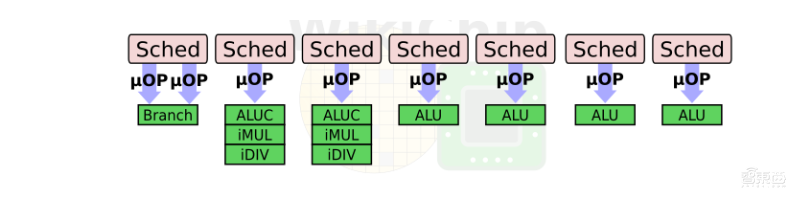

在后端,三星添加了两条新的32位整数ALU通道。这使整数通道(包括分支)的总数达到7个。添加两个32位ALU通道很有趣,因为它不会提高典型的简单ALU工作负载的吞吐量。

▲M5 ALU通道数情况

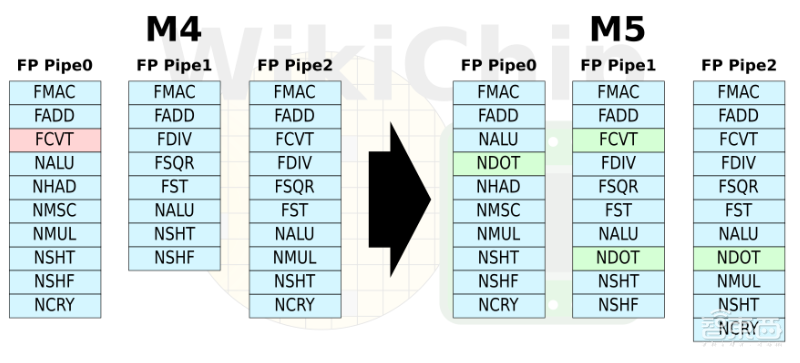

在浮点群集(floating-point cluster)方面,三星再次重新平衡了执行通道。最显著的变化是在三个FP通道的每一个上添加了neon dot生产执行单元。这样的改变可以帮助解释(explain)32b整数ALU。

▲M5 FP通道调整情况

结语:回归Arm架构,三星手机芯片寻找新发力点

从2015年第一代M1核心“Mongoose”亮相以来,三星已经推出了五代定制ARM核心。根据外媒报道,目前三星在CPU核心研发上的投入近200亿美元,Exynos系列SoC性能相较于骁龙、麒麟系列一直具有较强竞争力,此次“砍掉”自研核心业务,可能有多方因素影响。

三星虽然放弃了坚持多年的自研CPU核心的道路,但他们也在寻找其他方向。目前三星已经与AMD进行合作,利用AMD强大的GPU研发实力,发力手机GPU领域,预计2021年将会推出搭载AMD GPU的手机。

根据Canalys最新发布的数据看,2019年Q3三星仍然是全球最大的智能手机出货厂商,且出货量保持11%的增长速度,这位巨头在手机芯片领域近期动作频频,三星能否找到更多新的发力点,我们拭目以待。

原文来自:WikiChip Fuse