智东西(公众号:zhidxcom)

文 | 心缘

芯潮8月29日消息,今日,MIT和ADI公司的研究人员们创造了第一个完全可编程的16位碳纳米管微处理器。

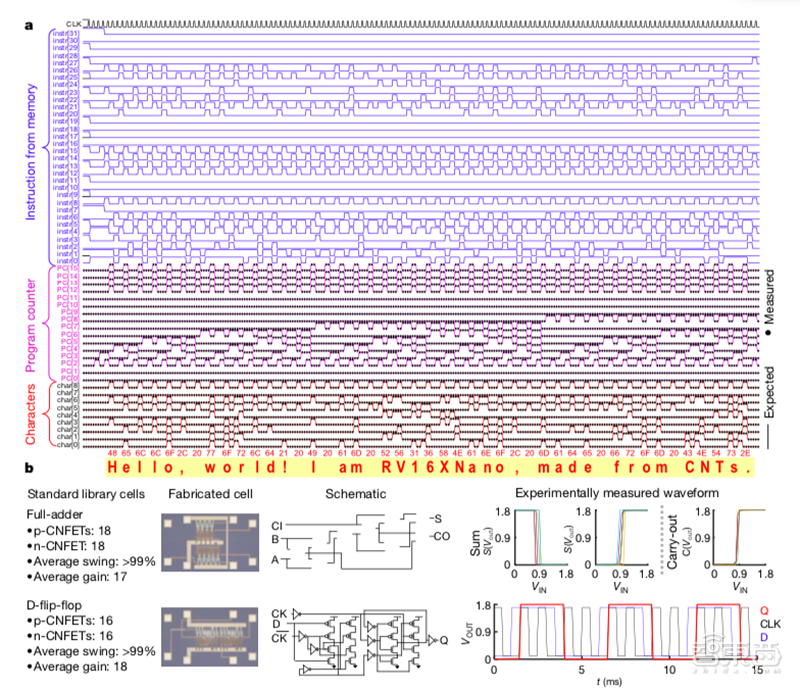

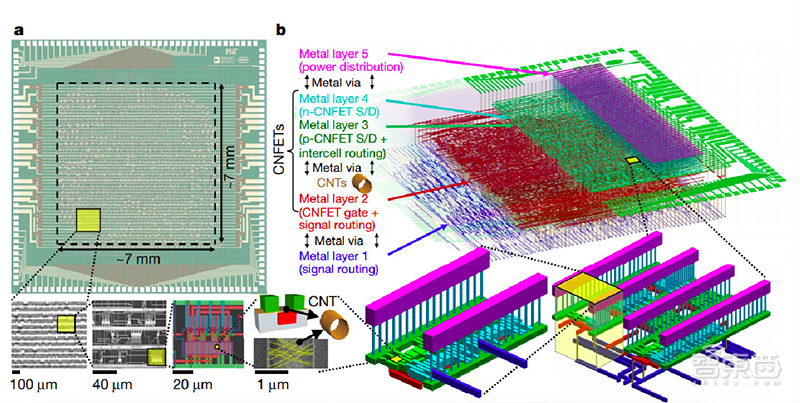

它是迄今基于碳纳米管的CMOS逻辑最复杂的集成,拥有14000多个晶体管,基于RISC-V架构,可执行与商用微处理器相同的任务。在测试中,它还执行了经典的“Hello World程序”:

“Hello, World! I am RV16XNano, made from CNTs.”

该芯片名为RV16X-NANO,70多页的制作工艺细节均在《Nature》上发表。

论文共同作者Max M.Shulaker表示,这是迄今为止由新兴纳米技术制成的最先进的芯片,有望用于高性能和高能效计算。

研究人员认为,这一芯片的设计和制造采用了行业标准,为超越硅的电子学指明了一个富有前景的发展方向。

研究人员们现已开始将这些制造工艺应用在硅芯片制造厂中,该研究由美国国防高级研究计划局(DARPA)资助。

关于碳纳米管芯片的上市时间,Shulaker表示,可能在五年内。

论文连接:https://www.nature.com/articles/s41586-019-1493-8

一、比硅能效高10倍的碳纳米管

在摩尔定律趋缓的压力中,研究人员一直在探索芯片设计和制造的新可能。

其中,碳纳米管场效应晶体管(CNFET)正是代替硅材料的首选,有望给芯片设计带来新的革命。

和硅相比,CNFET很容易地制成具有密集3D互连的多层,可将能效提升10倍,速度功耗都表现更好。

研究人员发现,金属碳纳米管对逻辑门的不同配对有不同的影响。

例如,A门中的一个金属碳纳米管可能会破坏A和B之间的连接,但B门中的几个金属碳纳米管可能不会影响A和B之间的任何连接。

经模拟实验,研究人员发现,所有不同的栅极组合对任何金属碳纳米管都是稳健的,而对任何金属碳纳米管都不具有鲁棒性。

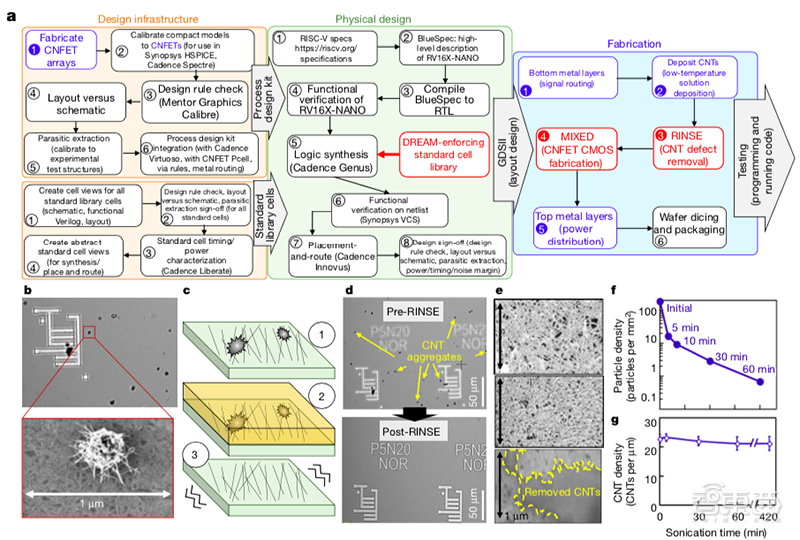

考虑到某些逻辑运算对金属纳米管的敏感度,MIT研究团队修改了开源RISC设计工具,定制了一个芯片设计程序,自动学习最不受金属碳纳米管影响的组合。

在芯片设计时,程序只利用稳健的组合,而忽略脆弱的组合,使得芯片中没有对金属碳纳米管最敏感的栅极。

RV16X-NANO芯片包含超过14000个晶体管,碳纳米管产率为100%;采用RISC-V架构指令集,能处理16位数据和32位指令,可完成与商用微处理器相同的任务。

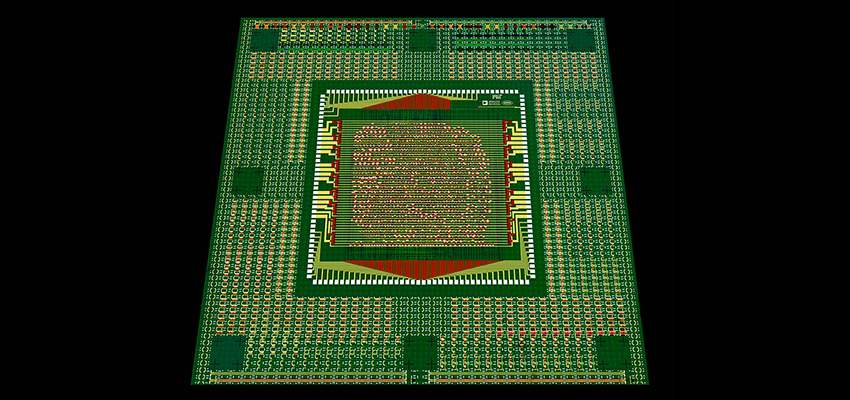

▲每个150mm晶圆片包括32个碳纳米管芯片

二、解决碳纳米管三大缺陷

不过,CNFET还存着一系列亟待跨越的难关,比如在大规模生产时,往往存在许多影响性能的缺陷。

MIT团队研发的芯片则在一定程度上解决了这些问题。

其微处理器是在上一个版本的基础上开发的,上一版本设计于六年前,只有178个碳纳米管,可执行1bit数据。

那时研究人员们就开始着手解决生产这种设备的三个具体挑战:材料问题、制作问题、功能问题。

1、材料:提纯放宽10000倍

碳纳米管需提纯至99.999999%,当前技术条件很难实现。

MIT研究人员提出一种叫DREAM(an acronym for “designing resiliency against metallic CNTs”)的技术,将碳纳米管的纯度要求降低降低了约4个数量级,即1万倍。

也就是说,纯度达99.99%即可制作芯片,当前技术是可以实现的。

2、制作:超大硅面,冲洗聚集体

至今将纳米管放置在特定精确位置的方法尚未被掌握,此前研究人员们常分别制作。

但这一过程会致使大量碳纳米管随机聚集在一起,并且其中会混入一些金属纳米管。

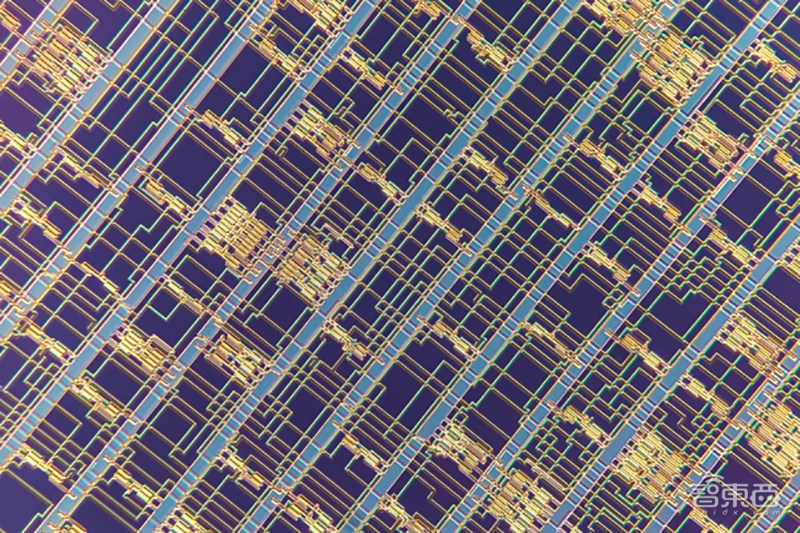

针对排列混乱问题,研究人员们制造了一个超大硅表面,可以保证碳纳米管在金属间隙生长。

为了去除聚集体,他们发明了一种名为RINSE的方法,即通过选择性剥离的方法移除生长的碳纳米管。

他们预先在晶片上涂抹一种试剂,以加强碳纳米管的贴附能力,把碳纳米管放上后,用某种特定聚合物包裹晶片,然后将其侵入某种溶剂,将聚集体带走,单个碳纳米管仍然粘在晶片上。

这样一来,他们就能将纳米管精确限制在定位区域。

和类似方法相比,这种技术可以将芯片上的颗粒密度降低250倍。

3、功能:精确调整P型/N型

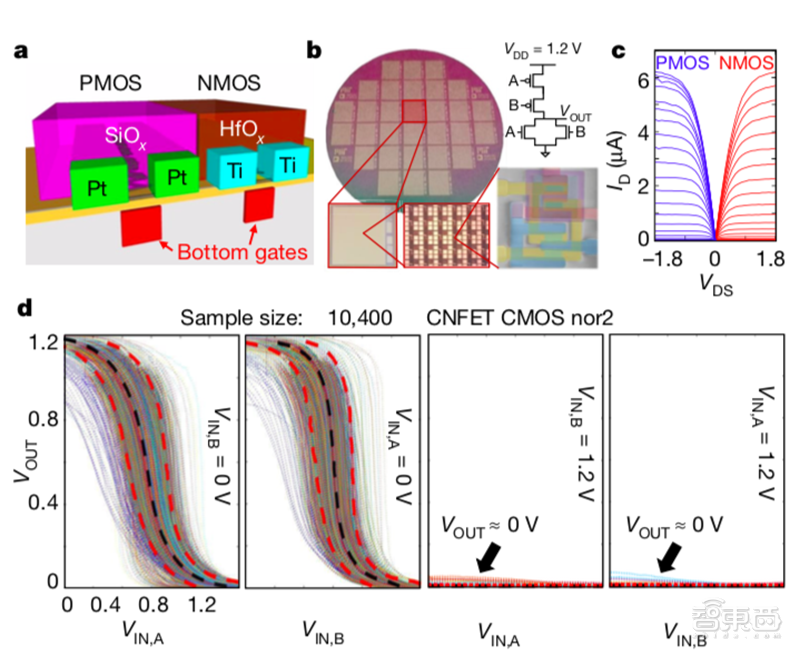

二进制计算需要两种晶体管:P型和N型。

P型或N型半导体在硅中通常通过掺杂少量其他元素实现,但碳纳米管很小,这种掺杂替代的方式对碳纳米管不起作用。

对此,MIT研究人员研发一种名为MIXED(金属表面工程与静电掺杂交叉)的技术,以精准地调整、优化晶体管的功能。

研究人员将金属氧化物附着在晶体管上,采用原子层沉积技术,根据需要操纵层的确切成分,将纳米管转化为P型或N型。

MIXED是一种低温工艺,因此晶体管可以构建在其他电路层之上而不会损坏它们。

事实上,RV16X-NANO中的晶体管内置于为晶体管提供电源的一层互连和另一层将晶体管连接到逻辑门和更大系统的层之间。

工程师对这方案相当感兴趣,它能释放空间,实现性能更好或更小的系统,但由于加工温度高,这一方案在硅中很难实现。

三、不足:承载电流不如硅芯片

RV16X-NANO芯片还存在不足之处。

其晶体管通道长度约为1.5微米,相当于1985年推出的硅处理器Intel 80386。

80386的运行频率为16MHz,而碳纳米管芯片最大频率只有1MHz,这一差异源于电子元件的电容以及晶体管可承载电流的能力。

增加电流的方法主要有三步:

1、减小晶体管通道长度

经证明,碳纳米管的通道长度可以缩小到5nm。

2、增加每个通道的纳米管密度

将每个通道中纳米管的密度从每微米10个增加到每微米500个。

对于随机分布的纳米管网络,可实现密度可能有上限,但新沉积技术可将这种网络的电流密度提升至1.7mA/μm 。

3、减小晶体管的宽度

从而减小源极和漏极的宽度,使电极更快地充电和放电。

结语:被学界看好的硅替代者

近些年,碳纳米管一直被学术界和工业界寄予厚望,期望它能成为硅的完美替代者,为芯片设计界掀起新的风暴。

从理论上讲,这种材料的制造速度和能耗均远优于硅芯片。

在应用方面,除了可以用在常见的笔记本、手机、物联网设备上,微处理器还可能探索更新的应用方向,比如可注射入体内的微型芯片、杀死人体内癌细胞的纳米机器等。

目前碳纳米管在分类、加工、排序、触头等方面还多有局限,如果能如Shulaker所言,碳纳米管芯片在五年内上市,那势必将会给全球半导体领域带了新的创新风潮。